- C 语言 是一种高级、顺序执行的软件编程语言,用于在通用处理器(CPU)上运行,告诉计算机“如何做”(How to do)。

- VHDL 是一种硬件描述语言,用于描述数字电路的结构和行为,最终目标是生成实际的硬件电路(逻辑门、触发器等),它描述的是“是什么”(What is)。

下面我们从多个维度进行详细的对比。

(图片来源网络,侵删)

核心定位与用途

| 特性 | C 语言 | VHDL |

|---|---|---|

| 语言类型 | 高级编程语言 | 硬件描述语言 |

| 核心用途 | 编写应用程序、操作系统、嵌入式软件等。 | 设计数字逻辑电路,如 FPGA、ASIC 芯片。 |

| 目标平台 | 通用处理器 | 硬件电路 |

| 设计思想 | 算法驱动:关注解决问题的步骤和算法。 | 结构/行为驱动:关注电路的组成和信号如何随时间变化。 |

执行模型与并行性

这是两者最根本的区别之一。

| 特性 | C 语言 | VHDL |

|---|---|---|

| 执行模型 | 顺序执行:代码从上到下逐行执行,除非遇到分支或循环。 | 并行执行:代码描述的是硬件的连接关系,大部分语句是同时执行的。 |

| 并行性 | 需要多线程/多进程等特殊机制来实现并行,是软件模拟的并行。 | 天然并行:电路中的各个逻辑门是同时工作的。process块之间是并行的,<=(信号赋值)是并发的。 |

| 时间概念 | 无时间概念:执行时间由CPU速度、编译器优化等因素决定,是抽象的。 | 有明确的时间概念:delta延迟(仿真时间步长)、after语句,精确描述信号传播的延迟。 |

例子:

- C语言:

a = 1; b = 2;先执行a=1,再执行b=2。 - VHDL:

a <= 1; b <= 2;在同一个process外,这两句是同时执行的,a和b在同一时刻被更新。

数据类型与变量

| 特性 | C 语言 | VHDL |

|---|---|---|

| 数据类型 | 丰富:int, float, char, struct, union, 指针 等,主要用于数据处理和计算。 |

与硬件紧密相关:std_logic (标准逻辑位), std_logic_vector (逻辑位向量), integer (整数), record (记录) 等。 |

| 变量 | int a;,用于存储计算结果。 |

信号:signal a : std_logic;,代表硬件中的物理连线,有传输延迟。变量: variable b : integer;,仅限于 process 内部使用,立即赋值,无延迟,用于临时计算。 |

| 赋值 | (赋值) | <= (信号赋值,有延迟) 或 (变量赋值,立即) |

控制结构

| 特性 | C 语言 | VHDL |

|---|---|---|

| 循环 | for, while, do-while,用于重复执行代码块。 |

for, while,主要用于描述硬件的迭代结构(如移位寄存器)。 |

| 分支 | if-else, switch-case,用于根据条件选择执行路径。 |

if-else, case,用于描述硬件中的多路选择器或条件逻辑。 |

| 关键区别 | 控制流是软件行为。 | 控制流描述的是硬件电路的结构。case 语句直接描述了一个多路选择器。 |

抽象层次

| 特性 | C 语言 | VHDL |

|---|---|---|

| 抽象层次 | 高:屏蔽了底层硬件细节(如寄存器、内存地址),开发者关注算法和逻辑。 | 可高可低: - 行为级:描述电路的功能(如计数器功能)。 - RTL级:最常用的层次,用寄存器、组合逻辑来描述电路。 - 门级/结构级:直接实例化逻辑门(AND, OR, NOT)来描述电路。 |

| 与硬件的关系 | 间接:代码被编译成机器码,由CPU解释执行。 | 直接:代码被综合工具转换成实际的逻辑门电路网表。 |

一个生动的比喻:建造房子

-

C 语言就像一份详细的施工步骤说明书:

- 先去搬砖块。

- 然后和水泥。

- 接着砌第一堵墙。

- ...(一步一步,顺序执行) 这份说明书告诉工人如何一步步完成房子,工人可以并行工作,但说明书本身是顺序的。

-

VHDL就像一份房子的建筑蓝图:

(图片来源网络,侵删)

(图片来源网络,侵删)- 这里有承重墙。

- 这里有窗户。

- 这里有电路连接图。

- 这里有一个厨房。 蓝图描述了房子的结构和组成,所有这些部分是同时存在的,建筑工人根据蓝图可以同时在不同区域施工,因为结构是并行的。

总结表格

| 特性 | C 语言 | VHDL |

|---|---|---|

| 本质 | 软件编程语言 | 硬件描述语言 |

| 目标 | 在CPU上运行的应用程序 | FPGA/ASIC芯片的数字电路 |

| 执行 | 顺序执行 | 并发/并行执行 |

| 时间 | 抽象的,由CPU决定 | 精确的,有延迟概念 |

| 数据 | 整型、浮点型、指针等 | std_logic, std_logic_vector 等 |

| 核心元素 | 变量、函数、循环、分支 | 信号、进程、实体、架构 |

| 设计方法 | 算法驱动 | 结构/行为驱动 |

| 最终产物 | 可执行文件 | 电路网表 |

两者如何结合?

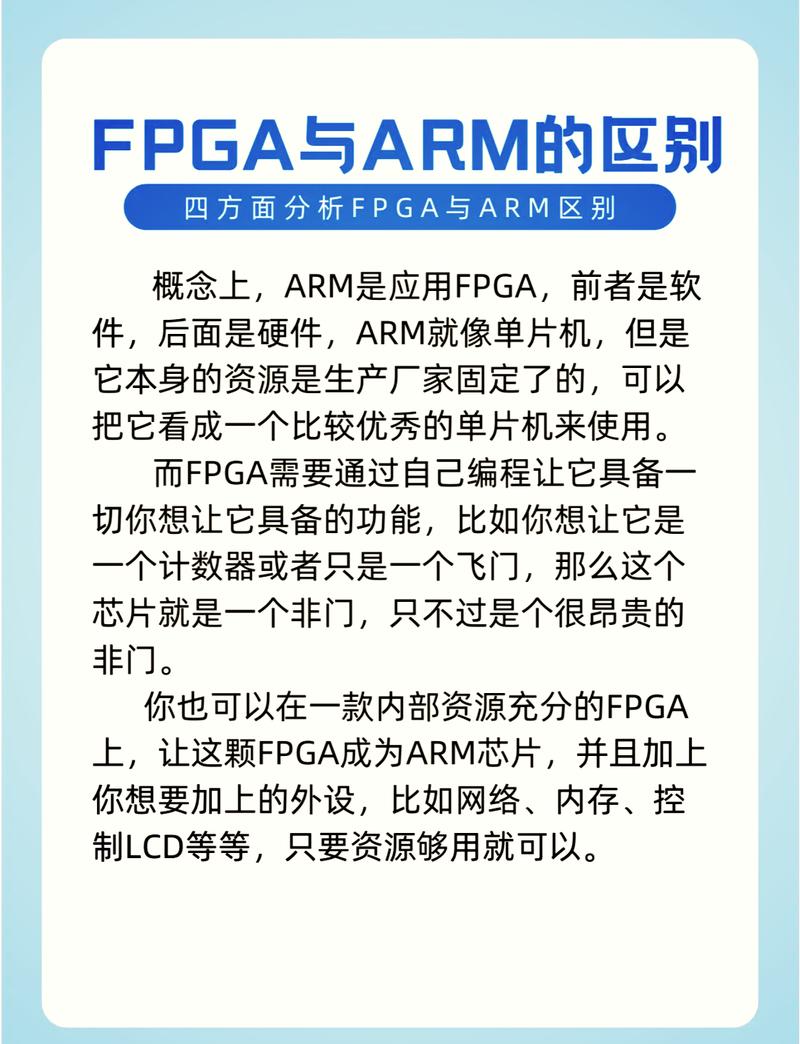

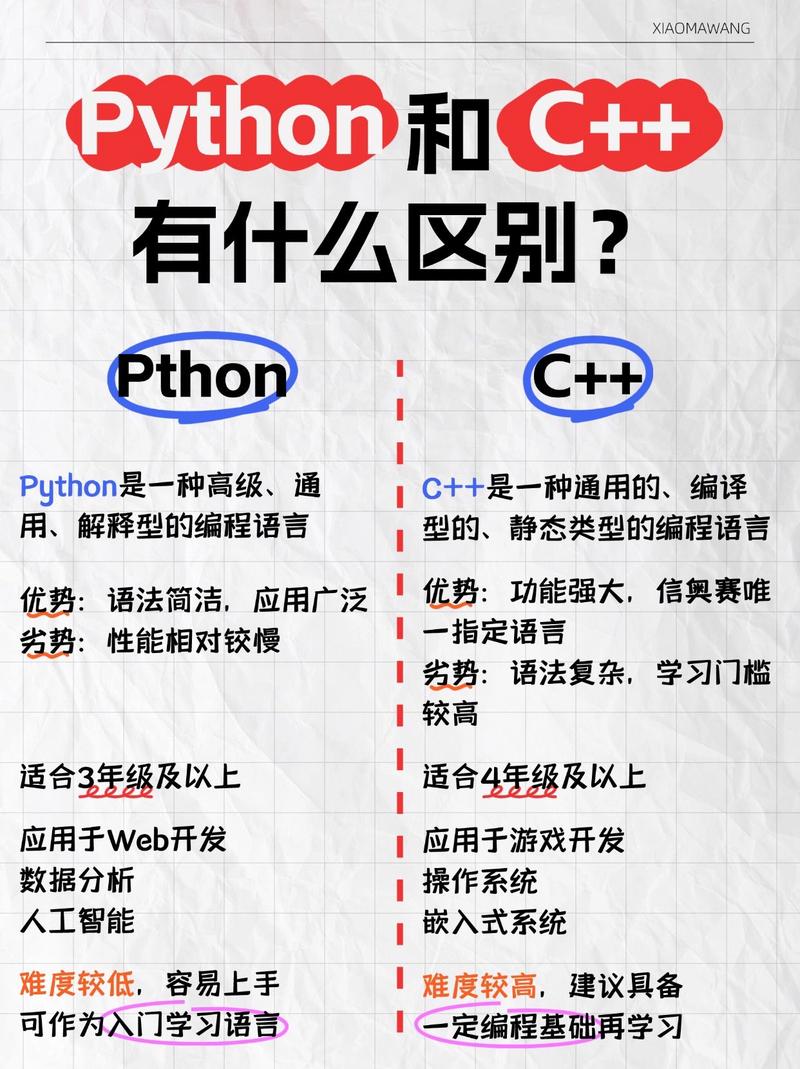

现代电子系统设计通常是软硬件协同设计,一个典型的SoC(片上系统)芯片内部,既有用VHDL设计的硬件加速器(如视频处理单元),也有用C/C++编写的软件运行在嵌入式CPU上(如ARM核)。

在这种情况下,C语言和VHDL通过一种叫做硬件/软件协同验证的技术结合在一起,软件部分(C代码)在模拟器上运行,硬件部分(VHDL代码)也在仿真器中运行,它们通过一个虚拟的总线模型进行通信,共同验证整个系统的功能是否正确。

(图片来源网络,侵删)