- C语言是告诉“计算机”如何一步一步地“做事”(顺序执行)。

- HDL是描述“硬件电路”长什么样(并发结构)。

下面我们从多个维度进行详细的对比。

(图片来源网络,侵删)

核心区别对比表

| 特性 | C语言 (C/C++) | HDL (Verilog/VHDL) |

|---|---|---|

| 设计目标 | 软件算法 | 硬件电路 |

| 描述软件的行为和算法,运行在通用处理器上。 | 描述硬件的结构和功能,用于逻辑门、寄存器、FPGA、ASIC等。 | |

| 思维方式 | 顺序、过程化 | 并发、结构化 |

| 代码从上到下顺序执行,强调“先做什么,再做什么”。 | 代码描述的是电路的同时存在的结构,所有模块在概念上是并行运行的。 | |

| 执行模型 | 指令驱动 | 事件驱动 |

| CPU取指、译码、执行,循环、分支等指令控制程序流程。 | 电路响应信号变化(电平跳变、时钟沿)而改变状态,由硬件物理结构决定。 | |

| 基本单元 | 变量、函数、循环、分支 | 模块、端口、线网、寄存器、组合逻辑、时序逻辑 |

| 变量存储在内存中,函数可以被调用。 | 模块代表一个硬件单元(如CPU核心、加法器),端口是输入/输出连接。 | |

| 时间模型 | 抽象的、无延迟 | 精确的、有延迟 |

a = b + c; 瞬间完成,不考虑CPU计算时间。 |

assign a = b + c; 描述组合逻辑,存在门级延迟。always @(posedge clk) 描述时序逻辑,延迟一个时钟周期。 |

|

| 并行性 | 需要多线程/多进程 | 天然并行 |

| 需要操作系统和编程语言的支持(如线程库)来实现并行。 | assign语句和多个always块之间是天然并行的,由硬件物理结构保证。 |

|

| 可综合性与可综合性 | 主要面向可执行 | 主要面向可综合 |

| C代码被编译成机器码,在CPU上运行。 | HDL代码需要被综合工具翻译成实际的逻辑门电路网表,部分HDL(如Verilog的$display)是不可综合的,仅用于仿真。 |

|

| 调试方式 | ||

| 软件调试:打印日志、断点、单步执行。 | 硬件调试:波形查看器、逻辑分析仪、FPGA在线调试。 | |

| 应用领域 | ||

| 操作系统、应用程序、驱动程序、嵌入式软件等。 | 数字IC设计、FPGA开发、验证平台、测试设备等。 |

详细解释与举例

设计目标:算法 vs. 结构

-

C语言: 你写一个排序算法,比如冒泡排序,你告诉CPU:“先比较第一个和第二个数,如果顺序不对就交换;然后比较第二个和第三个……直到最后一轮”,这是在描述一个过程。

// C语言:描述冒泡排序的过程 for (int i = 0; i < n-1; i++) { for (int j = 0; j < n-i-1; j++) { if (arr[j] > arr[j+1]) { // 交换 int temp = arr[j]; arr[j] = arr[j+1]; arr[j+1] = temp; } } } -

HDL: 你描述一个8位加法器,你告诉综合工具:“这个模块有两个8位输入

a和b,一个8位输出sum。sum的值在a和b的电平稳定后,经过几个门延迟后,就等于a + b”,你并没有描述“如何加”,而是描述了“加法器这个电路实体”。// Verilog:描述一个8位加法器的结构 module adder ( input [7:0] a, input [7:0] b, output [7:0] sum ); // assign 描述了一个组合逻辑结构 assign sum = a + b; endmodule

思维方式:顺序 vs. 并发

- C语言: 代码的执行顺序就是代码的书写顺序(除非有跳转语句)。

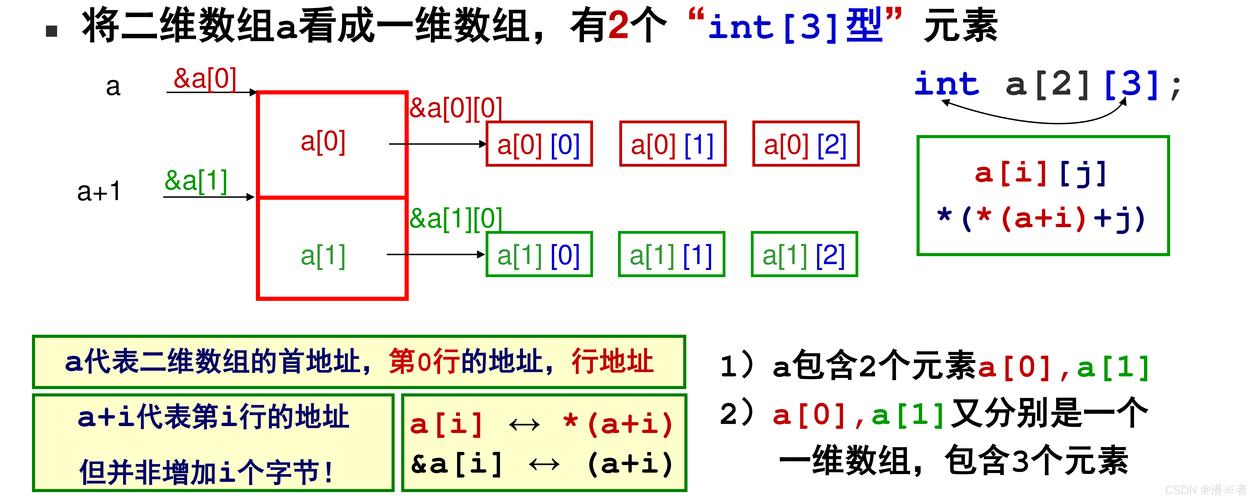

a=1; b=2;一定是a先赋值,b再赋值。 - HDL: 代码的书写顺序不代表执行顺序,下面的两个

assign语句是并发执行的,它们描述了两个独立的电路。// 这两个assign是同时发生的,没有先后顺序 assign out1 = in1 & in2; // 描述一个与门 assign out2 = in1 | in2; // 描述一个或门

同样,两个

always块也是并发运行的,它们可以响应不同的信号,代表电路中两个独立的时序逻辑单元。

执行模型:指令 vs. 事件

- C语言: CPU不断地执行指令流。

while(1){...}会让CPU在一个循环里空转,消耗CPU周期。 - HDL:

always @(posedge clk)描述的是一个在时钟上升沿触发的寄存器,当时钟没有上升沿时,这个块里的代码是“静止”的,不消耗任何“能量”,它只在事件(时钟边沿)发生时才被激活。// 这个块只在clk的上升沿执行一次,然后进入等待状态 always @(posedge clk) begin reg <= data_in; // 在时钟上升沿,将输入数据锁存到寄存器中 end

延迟:抽象 vs. 精确

- C语言:

c = a + b;的执行时间取决于CPU的架构、指令集和流水线,但在代码层面是不可见的,程序员通常不关心单个加法需要多少纳秒。 - HDL: 延迟是设计的核心部分。

#5 a = b;表示在5个时间单位后,a的值才变为b,在综合时,工具会根据你描述的逻辑推断出固有的门延迟,时序分析是数字电路设计中至关重要的一步,确保电路能在规定时钟频率下稳定工作。

总结与类比

你可以把一个数字系统想象成一个餐厅:

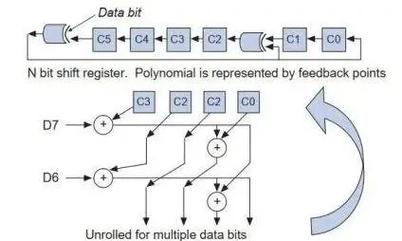

(图片来源网络,侵删)

- C语言程序员就像是餐厅经理,他制定流程:

顾客点单 -> 2. 厨房做菜 -> 3. 服务员上菜 -> 4. 顾客结账,他关心的是工作流程和顺序。 - HDL工程师就像是餐厅建筑师,他设计餐厅的布局:

收银台在这里,厨房在那里,有5张桌子,每张桌子配2把椅子,他关心的是物理结构和空间布局,收银台和厨房可以同时工作(并行),从厨房到桌子的上菜时间需要考虑(延迟)。

C语言和HDL在现代电子系统中是紧密协作的:

- 顶层设计:用HDL(如Verilog)设计一个SoC(System on Chip)的整体结构,包括CPU核心、内存控制器、外设接口等。

- 软件实现:用C语言(或C++)为这个SoC编写操作系统、驱动程序和应用程序。

- 协同验证:用HDL编写一个“测试平台”,将用C语言编译成的程序(通常是机器码)加载到HDL描述的CPU模型中运行,通过仿真来验证整个软硬件系统是否正确工作。

这种软硬件协同设计的方式是当今芯片和电子产品开发的主流模式。

(图片来源网络,侵删)